改善短溝道效應的方法分享-KIA MOS管

信息來源:本站 日期:2026-01-13

當金屬氧化物半導體場效應晶體管(MOSFET)的溝道長度(L)縮減至與耗盡區(qū)寬度相近時,器件的電學特性,諸如閾值電壓VT、亞閾值擺幅SS以及漏電流leakage current等,會顯著偏離長溝道時的行為。

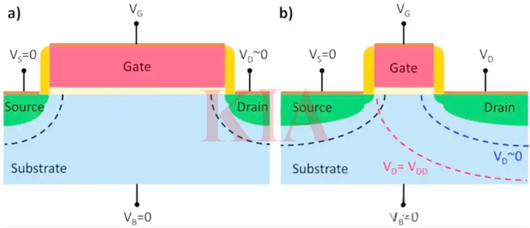

如圖所示,在MOSFET中,由源極和漏極擴散區(qū)域所形成的耗盡區(qū),會向摻雜濃度較低的結(jié)處,即襯底方向延伸。對于長溝道晶體管,其耗盡區(qū)的延伸與柵極總長度相比可忽略不計,因此對晶體管電學特性的影響也極小。

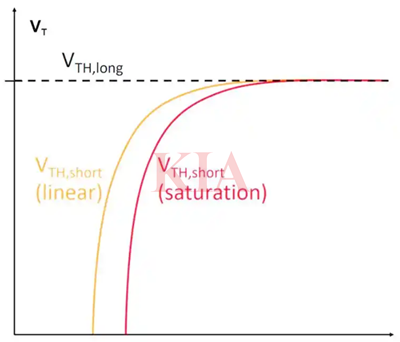

然而,隨著柵極長度的縮減,耗盡區(qū)的延伸長度與溝道長度相當,導致柵極對溝道的控制能力部分喪失。這一變化進而引發(fā)了短溝道效應中的“閾值電壓滾降(VTH roll-off)”現(xiàn)象。

漏致勢壘降低效應

此外,當在漏極施加偏壓(通常源極接地)時,漏極擴散區(qū)域的耗盡區(qū)會在溝道內(nèi)進一步加深,這會導致有效柵極長度減小,即溝道長度調(diào)制效應。因此,在VDS等于VGS減去閾值電壓以上時,電流不會達到飽和狀態(tài)。隨著VDS值的進一步增大,漏極耗盡區(qū)會向襯底方向進一步延伸,直至與源極耗盡區(qū)發(fā)生重疊。

這一系列變化在短溝道晶體管中會導致柵極對溝道的控制能力進一步削弱。由于強漏極偏壓引發(fā)的源極/漏極耗盡區(qū)重疊,會使Source與Bulk結(jié)處的勢壘降低,從而引發(fā)閾值電壓的降低,這種閾值電壓的降低現(xiàn)象被稱為漏致勢壘降低(DIBL)效應。

閾值電壓降低與漏電流增加

Vth降低的原因:隨著溝道長度的減小,柵極電場對溝道的控制能力逐漸減弱,而漏極電場對溝道電勢分布的影響則逐漸增強。

Vth降低的影響:可能導致器件在關態(tài)時的漏電流增加,進而影響電路的靜態(tài)功耗和噪聲容限。

漏電流增加的原因:Vth的降低會導致亞閾值區(qū)域的漏電流顯著上升,同時,源漏電阻的降低也會進一步加劇漏電流的問題。

漏電流增加的影響:直接導致靜態(tài)功耗的上升,從而影響移動設備的電池壽命。

驅(qū)動電流的變化

在溝道長度減小的初期,驅(qū)動電流會因溝道電阻的降低而有所增加。然而,隨著溝道長度的進一步減小,遷移率的下降和漏電流的增加可能會抵消這種驅(qū)動電流的增加,甚至導致驅(qū)動電流的下降。驅(qū)動電流的變化將直接影響器件的開關速度和整體電路的性能。

優(yōu)化摻雜工藝

調(diào)整溝道區(qū)摻雜濃度和分布:通過精確控制溝道區(qū)的摻雜濃度和分布,可以有效調(diào)節(jié)晶體管的電學特性,從而減小短溝道效應的影響。例如,采用漸變摻雜技術可以使得溝道區(qū)的摻雜濃度從源極到漏極逐漸變化,有助于抑制漏電流的增大。

使用高-k介質(zhì)和低功函數(shù)金屬柵極:高-k介質(zhì)可以提高柵氧化層的電容密度,而低功函數(shù)金屬柵極可以降低柵極的開啟電壓,從而在一定程度上補償由于溝道長度縮短而導致的閾值電壓下降。

改進晶體管結(jié)構(gòu)

三維晶體管(如FinFET):通過引入三維結(jié)構(gòu),可以增加晶體管的導電通道面積,從而在保持較小溝道長度的同時提高器件的性能。FinFET等三維晶體管結(jié)構(gòu)能夠有效抑制短溝道效應,提高電路的集成度和穩(wěn)定性。

多柵極晶體管:通過在晶體管中引入多個柵極來控制溝道中的電荷分布,可以進一步減小短溝道效應的影響。這種結(jié)構(gòu)能夠更精確地調(diào)控溝道中的電場分布,從而提高晶體管的開關速度和穩(wěn)定性。

應用先進的制造工藝

原子層沉積(ALD):利用ALD技術可以精確控制薄膜的厚度和均勻性,從而制備出高質(zhì)量的柵氧化層和界面層。這有助于減小柵極泄漏電流和界面態(tài)密度,進而改善短溝道效應。

電子束光刻(EBL):EBL技術可以實現(xiàn)高精度的圖案轉(zhuǎn)移,用于制造具有更小尺寸的晶體管。通過減小晶體管的物理尺寸,可以在一定程度上緩解短溝道效應帶來的問題。但需要注意的是,過小的尺寸也可能導致其他新的問題出現(xiàn),因此需要綜合考慮各種因素進行優(yōu)化設計。

聯(lián)系方式:鄒先生

座機:0755-83888366-8022

手機:18123972950(微信同號)

QQ:2880195519

聯(lián)系地址:深圳市龍華區(qū)英泰科匯廣場2棟1902

搜索微信公眾號:“KIA半導體”或掃碼關注官方微信公眾號

關注官方微信公眾號:提供 MOS管 技術支持

免責聲明:網(wǎng)站部分圖文來源其它出處,如有侵權請聯(lián)系刪除。